## FPGA Pulse Monitor in a Laboratory Test Environment

A Thesis Presented to

The Faculty of the Computer Science Program

California State University Channel Islands

In (Partial) Fulfillment

of the Requirements for the Degree

Masters of Science in Computer Science

by

Susan Portugal

May 2014

Master Thesis by Susan Portugal

© 2014 Susan Portugal ALL RIGHTS RESERVED Master Thesis by Susan Portugal

### APPROVED FOR THE COMPUTER SCIENCE PROGRAM

5 Advisor: Dr William Wolfe Date 5 Dr AndrzejBieszczad Date

Dr Peter Smith

Date

4

5/21/1

### APPROVED FOR THE UNIVERSITY

5-21-14 Dr Gary A. Berg Date

#### **Non-Exclusive Distribution License**

In order for California State University Channel Islands (CSUCI) to reproduce, translate and distribute your submission worldwide through the CSUCI Institutional Repository, your agreement to the following terms is necessary. The authorts retain any copyright currently on the item as well as the ability to submit the item to publishers or other repositories.

By signing and submitting this license, you (the author's' or copyright owner) grants to CSUCI the nonexclusive right to reproduce, translate (as defined below), and/or distribute your submission (including the abstract) worldwide in print and electronic format and in any medium, including but not limited to audio or video.

You agree that CSUCI may, without changing the content, translate the submission to any medium or format for the purpose of preservation.

You also agree that CSUCI may keep more than one copy of this submission for purposes of security, backup and preservation.

You represent that the submission is your original work, and that you have the right to grant the rights contained in this license. You also represent that your submission does not, to the best of your knowledge, infringe upon anyone's copyright. You also represent and warrant that the submission contains no libelous or other unlawful matter and makes no improper invasion of the privacy of any other person.

If the submission contains material for which you do not hold copyright, you represent that you have obtained the unrestricted permission of the copyright owner to grant CSUCI the rights required by this license, and that such third party owned material is clearly identified and acknowledged within the text or content of the submission. You take full responsibility to obtain permission to use any material that is not your own. This permission must be granted to you before you sign this form.

IF THE SUBMISSION IS BASED UPON WORK THAT HAS BEEN SPONSORED OR SUPPORTED BY AN AGENCY OR ORGANIZATION OTHER THAN CSUCI, YOU REPRESENT THAT YOU HAVE FULFILLED ANY RIGHT OF REVIEW OR OTHER OBLIGATIONS REQUIRED BY SUCH CONTRACT OR AGREEMENT.

The CSUCI Institutional Repository will clearly identify your name(s) as the author(s) or owner(s) of the submission, and will not make any alteration, other than as allowed by this license, to your submission.

| FPGA         | PULSE | MONITOR | IN | A     | LABORATORY | TEST | ENVIRONMENT |

|--------------|-------|---------|----|-------|------------|------|-------------|

| Title of Ite | m     |         |    | 1.000 |            |      | -           |

FPGA PULSE MONITOR

3 to 5 keywords or phrases to describe the item

Name (Print)

\_

Author's Signature

This is a permitted, modified version of the Non-exclusive Distribution License from MIT Libraries and the University of Kansas. F

### FPGA Pulse Monitor in a Laboratory Test Environment

by Susan Portugal Computer Science Program California State University Channel Islands

#### Abstract

Manufacturers often resort to Application-Specific Integrated Circuits (ASIC) to meet their specific end-product requirements. Although ASICs are very effective in many applications, they have significant limitations. In particular, designers are often faced with a performance cost trade-off. To get the performance they desire, designers often come up with costly ASIC designs. This clash between cost and performance has encouraged the evolution of new technology, pushing toward a more flexible, costeffective, solution. This thesis will demonstrate how the integration of specialized hardware, Field-Programmable Gate Arrays (FPGA), programmed as a pulse monitor for capturing digital signals, and a graphical user interface (GUI) can provide low a cost solution with greater flexibility, increased data collection/storage, improved portability, higher efficiency, and enhanced performance.

#### Acknowledgements

The author would like to thank the faculty at California State Channel Islands University, employer (Engility Corp.), and family for their support.

### **TABLE OF CONTENTS**

| CHAPTER 1: INTRODUCTION                                               |    |

|-----------------------------------------------------------------------|----|

| $1_{ m s}1$ Purpose of the Project                                    | 7  |

| 1.2 Available Solutions                                               |    |

| 1.3 HISTORY OF FPGA                                                   |    |

| CHAPTER 2: CURRENT APPLICATIONS OF FPGAS - WHERE FPGAS ARE USED TODAY | 12 |

| 2.1 FPGA DEFINITIONS                                                  |    |

| 2.2 FPGA Architecture                                                 |    |

| CHAPTER 3: FPGA MANAGEMENT: VERILOG AND VHDL SOFTWARE                 | 17 |

| CHAPTER 4: PULSE MONITOR PROJECT DETAILS                              | 18 |

| 4.1 Pulse Monitor Overview                                            |    |

| 4,2 Hardware                                                          | 18 |

| 4,2,1 Hardware Code                                                   |    |

| 4,2,2 Verilog Code                                                    |    |

| 4,3 Software Code                                                     | 26 |

| 4,3,1 VISUAL STUDIO C# CODE                                           |    |

| 4 4 Pulse Monitor Enhancements                                        |    |

| 4 4,1 Multi-Channel Single Ended Input Signal Pulse Monitor           | 28 |

| 4 4 2 Multi-Channel Differential Input Signal Pulse Monitor           |    |

| 4 4.3 Expanded One Channel Pulse Monitor with Decoding                | 35 |

| 4 4 4 Pulse Stream Decoding                                           |    |

| CHAPTER 5: EXPERIMENTS                                                | 39 |

| CHAPTER 6: ANALYSIS OF RESULTS                                        |    |

| CHAPTER 7: CONCLUSION                                                 | 45 |

| 7,1 Pulse Monitor for Other Applications                              |    |

| CHAPTER 8: FUTURE WORK                                                | 47 |

### LIST OF FIGURES

| Figure 1.  | Agilent DSOX92004A Infiniium High-Performance Oscilloscope       | . 8 |

|------------|------------------------------------------------------------------|-----|

| Figure 2.  | Agilent DSO1052B Oscilloscope                                    | . 8 |

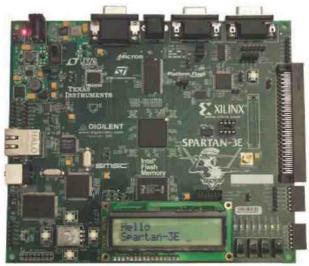

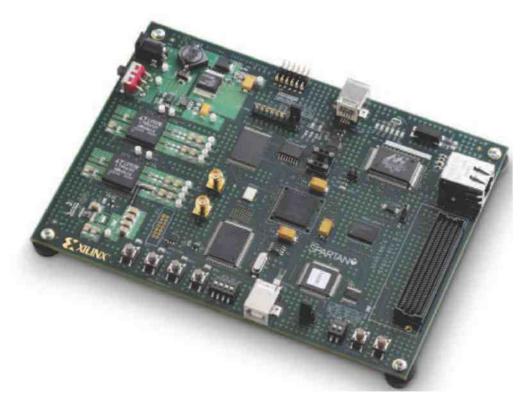

| Figure 3.  | Spartan 3E Starter Kit                                           |     |

| Figure 4.  | Spartan 6 FPGA Chip                                              | 10  |

| Figure 5.  | FPGA Timetable (4)                                               | 11  |

| Figure 6.  | Table of Common FPGA Applications (5)                            | 12  |

| Figure 7.  | Key Terms (6)                                                    | 13  |

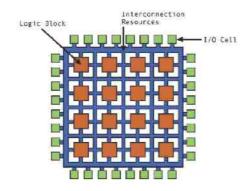

| Figure 8.  | Typical FPGA Structure (7)                                       | 14  |

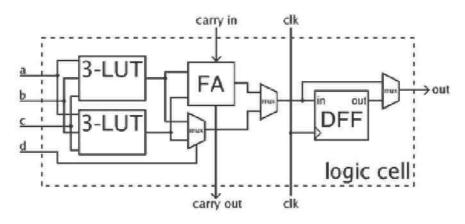

| Figure 9.  | Basic Illustration of a Logic Cell (1)                           | 14  |

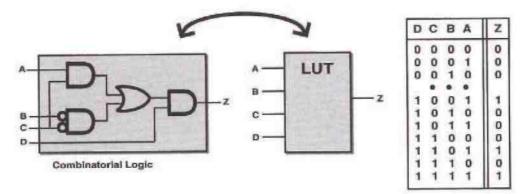

| Figure 10. | LUT (8)                                                          | 15  |

| Figure 11. | Xilinx CLB Comparison                                            | 15  |

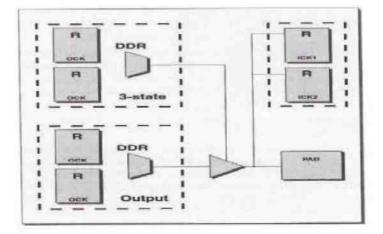

| Figure 12. | I/O block structure (8)                                          | 16  |

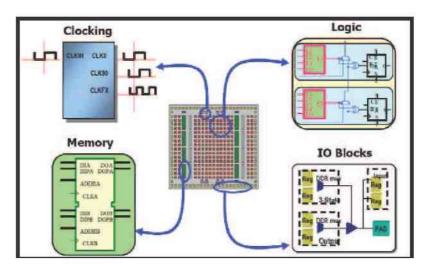

| Figure 13. | Basic FPGA Architecture (8)                                      | 16  |

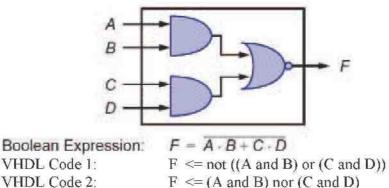

| Figure 14. | Diagram of Boolean Expression Represented in VHDL & Verilog (10) | 17  |

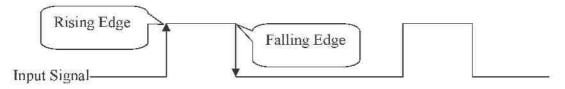

|            | Digital Signal                                                   |     |

| Figure 16. | Spartan-6 FPGA SP601 Evaluation Kit (11)                         | 19  |

|            | SP601 Evaluation Kit Specifications (11)                         |     |

|            | Xilinx ISE Project Navigator (14)                                |     |

| Figure 19. | Xilinx ISE iMPACT                                                | 21  |

|            | Edge Detection by D Flip-Flops (17)                              |     |

|            | Pulse Monitor Example Input Timing Diagram                       |     |

| -          | Verilog Code for Edge Detection                                  |     |

| Figure 23. | Verilog Code for Channel Selection for Output Message            | 25  |

| -          | C# Send Packet (16)                                              |     |

|            | C# Ethernet Filter and Message Type Filter (16)                  |     |

|            | Pulse Monitor GUI                                                |     |

|            | SP601 Evaluation Board with J13                                  |     |

| -          | Verilog Changes for Multi-Channel Pulse Monitor                  |     |

|            | Visual Studio C# Changes for Multi-Channel Pulse Monitor         |     |

|            | Multi-Channel Pulse Monitor GUI                                  |     |

|            | Xilinx FMC XM105 Debug Card (19)                                 |     |

|            | Differential Input Verilog Code (20)                             |     |

|            | UCF Changes for Multi-Channel Pulse Monitor                      |     |

|            | VITA 57.1 FMC LPC Connections on SP601                           |     |

|            | SP601 Board Connection to Connector J1 on FMC XM105 Debug Card   |     |

|            | Verilog Code for 54 Pulse Edge Detection                         |     |

|            | Example Pulse Stream Sequence                                    |     |

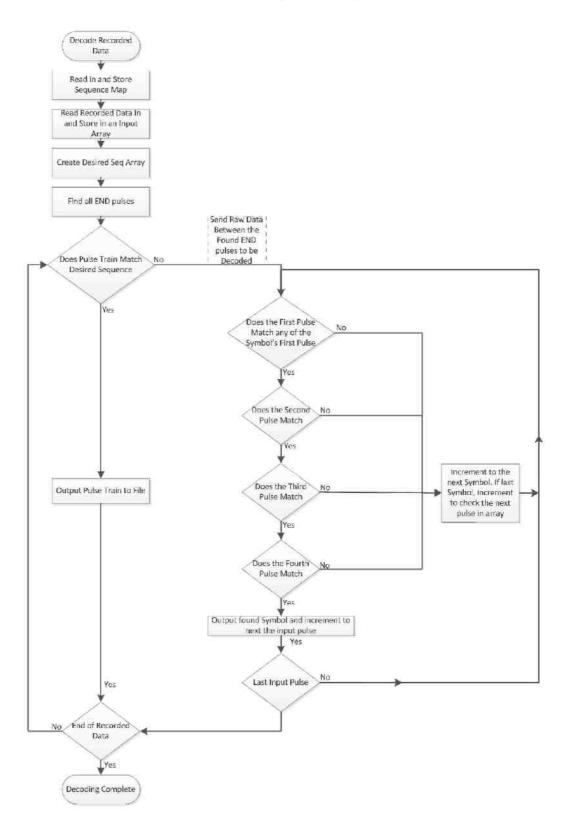

|            | Pulse Train Decoding Flow Diagram                                |     |

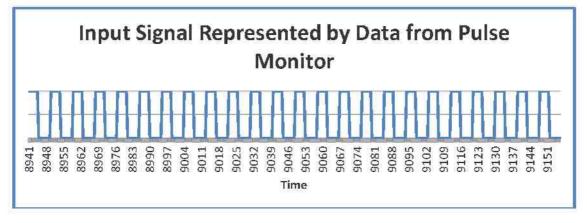

| Figure 39. | Pulse Data from Output File (100 Hz with 50% Duty Cycle)         | 39  |

| -          | Input Signal Graph (100 Hz with 50% Duty Cycle)                  |     |

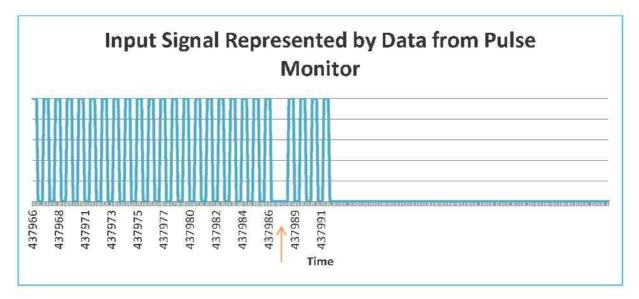

| Figure 41. | Pulse Data from Output File (1 kHz with 50% Duty Cycle)          | 41  |

| -          | Input Signal Graph (1kHz with 50% Duty Cycle)                    |     |

| Figure 43. | Pulse Monitor Slice Usage                                        | 44  |

# **Chapter 1: Introduction**

Field-programmable gate array (FPGA) is a custom, user-designed, programmable logic chip. Prior to the introduction of the FPGA, the primary computer based application involved an application specific integrated circuit (ASIC). The production and application of these circuits were typically very expensive, very user specific and generally intended for high volume use, due primarily to the limited number of manufacturers. Once manufactured, they were un-changeable, and not subject to correction in the event errors were made during manufacture. However, with the vast expansion of computer based applications, it became increasingly necessary and obvious, that the need for a more user adaptable chip was necessary, in order to meet the demands of the end-user. Thus, the emergence of the FPGA; an integrated circuit that allows a user to customize by programming for their specific need. (1)

The importance of the emergence of the FPGA in today's rapidly evolving computer age cannot be overstated. Nonetheless, as with most systems, the system is only as good as the operator; in this case, the programmer. Integrating appropriate software applications, while utilizing generally common hardware devices, together with a FPGA, can result in a generally very cost effective unit, compatible to a multitude of tasks and environments, that is particularly user friendly, and typically, time efficient.

### **1.1 Purpose of the Project**

In a laboratory environment that performs hardware and systems analysis, it is essential that test equipment, software simulations, and procedures be adaptable to the ever changing requirements that modern technology demands. Deadline driven projects and tight budget constraints fuel the necessity for efficient use of time, money, and physical assets. An FPGA can prove to be a valuable solution to many challenges that arise during the development and testing of new systems. In this case, there was a requirement to monitor multiple signals coming from a system component, perform calculations based on the signals, capture the calculated data in a file, and display the data to the end user. Capturing necessary digital signals, TTLs (Transistor-Transistor Logic signals) data was proving to be very inefficient, costly, and troublesome, in that not all data was being captured. There had to be a better means to capture, and retain necessary data without incorporating more high costs and sensitive equipment (oscilloscopes) to fit the demands of the user. The goal of this project is to use an FPGA as a timely, cost effective, and feasible solution to meet the requirements of the system under test, through the integration of a FPGA (Pulse Monitor).

The project initiated at my work site involves signal data collection. However, due to the proprietary and classified nature of the project, I am not able to discuss the true nature or purpose of this project, nor am I allowed to divulge specific data. Nonetheless, enough information will be discussed to allow for the understanding and project importance.

## **1.2 Available Solutions**

There are three readily available solutions to monitor digital input signals. The first is an Agilent DSOX92004A Infiniium High-Performance Oscilloscope which cost \$177,341 as seen in Figure 1. This oscilloscope is a very valid solution; however, there is a limit to the amount of data that is saved due to the scope saving all parametric data of the input signal, and with its stated cost, not a very cost effective solution. In addition to the state limitations, oscilloscopes usually only have two to four maximum inputs.

Figure 1. Agilent DSOX92004A Infiniium High-Performance Oscilloscope

The second solution is a lower cost oscilloscope, Agilent DSO1052B Oscilloscope, Figure 2, which cost \$512.

Figure 2. Agilent DSO1052B Oscilloscope

This oscilloscope allows users to view the input pulses; however, there are no means to be able to continuously save all data.

The last available solution is a Spartan 3E Starter Kit which cost \$199 as seen in Figure 3.

Figure 3. Spartan 3E Starter Kit

This solution was used but, the Spartan 3E Starter Kit was found to be very cumbersome. Input channels were selected by having to slide the switches on the board and required the user to view the data on the LCD panel located on the board. This was a very simple initial approach to solving the project requirements, however due to the size of the FPGA slices, not all requirements could be met.

## **1.3 History of FPGA**

The first commercially available FPGA was invented in 1985. Up until 1985, the bulk of computer chip manufacturers were primarily interested in the mass production of chips. This was a very lucrative industry as the development of the chips was primarily a domestic venture, which dominated the global semi-conductor market. With little competition, cost remained high and out of the hands of many potential users. Low cost Asian manufacturers slowly began entering the market. This got the attention of US manufacturers as they began losing their market share. Simultaneously, with the market beginning to open up to more users, chip consumers began demanding more "specialized chips that could be utilized for specific applications". (2)

Most chip manufacturers were very reluctant to enter this application-specific market. Designing and manufacturing an array of different chips, meant that they could only be marketed primarily to smaller markets, and generally, at a smaller monetary return when compared to mass produced chips. The limited number of manufacturers, coupled with their reluctance to meet the demands of the consumer, resulted in the frustration of these application-specific circuit consumers. The few circuits that were made were often at a high cost and also at the mercy of the manufacturer. If there were defects in the chips, or if the needs of the consumer changed, the wait time to address the issues was often lengthy. This hold up could in turn equate to a loss of millions of dollars due to project stalls. (2)

During this time, Ross Freeman was working as a chip engineer at Zilog Corporation, a subsidiary of Exxon Corporation. Freeman realized that there might be a better way of meeting the need for application-specific circuits. His idea was to develop a sort of "blank computer chip that could be programmed by the customer." This technology later became known as "field programmable gate array" or FPGA.(2) Figure 4 is a Xilinx Spartan 6 FPGA Chip.

Figure 4. Spartan 6 FPGA Chip

Risks associated with faulty chips, could therefore be minimized and, in turn, allow for much greater flexibility for companies designing equipment that incorporated the chips. Freeman, who was a vice-president and general manager at Zilog at the time, approached his superiors and suggested that the development of FPGA devices could be a viable new avenue for Zilog. However, he was unable to convince executives at Exxon that his idea had merit

Freeman later left his position with Zilog. He teamed up with another former Zilog employee, Bernard Vonderschmitt. Together, in February 1984, they founded Xilinx and in 1985, the first FPGA was commercially marketed. The company's system basically consisted of an "off-the-shelf programmable chip and a software package that could be used to program and tailor the chip for specific needs." The technology was based on the arrangement of gates (the lowest level building block in a logic circuit) in complex formations called arrays; as the number of gates increased, the more complex were the functions that the semiconductor could perform.

Computer applications during this time (late 1980's and in the 1990s) continued to increase and with it, the market for application-specific circuits. Subsequently, the market for FPGA chips also increased substantially, resulting in both revenue and profit growth for Xilinx. "Sales rose to nearly \$30.5 million in 1988 (fiscal year ended March 30, 1989) before rising to \$50 million in 1989. Xilinx posted its first surplus—a net income of \$2.92 million—in 1988 and went on to generate profits of \$6 million in 1989." (2) Approximately 70% of Xilinx market, at this time, was primarily domestic, and in 1990 sold approximately \$100 million worth of its products. Xilinx customers included "Apple Computer, IBM, Compaq, Hewlett-Packard, Fujitsu, Sun Microsystems, and Northern Telecom." Although there were other companies such as Actel and Altera Corporation selling technology that was similar to FGPA systems, Xilinx essentially controlled 100% of the FPGA market during the mid-1990. However, as most innovations breed competition, Xilinx dominance eroded, causing Xilinx to continue to

evolve/improve their technology in the form of introducing different "families" of FPGA chips and software, to "complement low-power applications/low-power devices such as portable and wireless communication gear, and digital cameras." By the end of 1996, Xilinx was employing more than 1,000 workers throughout North America, Asia, and Europe, selling more than 40 varieties of programmable logic products, with revenues of approximately \$550 million. (2)

The 1990s were an explosive period of time for FPGAs, both in sophistication and the volume of production. In the early 1990s, FPGAs were primarily used in telecommunications and networking. By the end of the decade, FPGAs found their way into consumer, automotive, and industrial applications. (3) Figure 5 contains an FPGA timetable from *Field-Programmable Gate Array Explained*.

| Year                                           | Market Size                                         |  |

|------------------------------------------------|-----------------------------------------------------|--|

| 1985                                           | First commercial FPGA technology invented by Xilinx |  |

| 1987                                           | \$14 million                                        |  |

| ~1993                                          | >\$385 million                                      |  |

| 2005                                           | \$1.9 billion                                       |  |

| 2010 estimates                                 | \$2.75 billion                                      |  |

| 146<br>                                        |                                                     |  |

| Year                                           | Gates                                               |  |

| <b>1987</b> 9,000 gates, Xilinx                |                                                     |  |

| 1992 600,000, Naval Surface Warfare Department |                                                     |  |

| Early 2000s                                    | Millions                                            |  |

|                                                |                                                     |  |

| Year                                           | FPGA Design Starts                                  |  |

| 1990's                                         | 10,000                                              |  |

| 2005                                           | 80,000                                              |  |

| 2008                                           | 90,000                                              |  |

| <b>2010</b> Estimated > 110,000                |                                                     |  |

Figure 5. FPGA Timetable (4)

# **Chapter 2: Current Applications of FPGAs – Where FPGAs are Used Today**

Due to their programmable nature, FPGAs are adaptable to various uses and markets. A small portion of uses or applications of FPGAs today are included in Figure 6 below.

| Aerospace and Defense | Automotive                                           | Switches and Routers    |

|-----------------------|------------------------------------------------------|-------------------------|

| Avionics              | Digital Signal Processing                            | Digital Cameras         |

| Space                 | Image Processing                                     | Printers                |

| Audio                 | Broadcast                                            | Servers                 |

| Security Systems      | Medical (Ultrasound, MRI,<br>X-ray, PET, CT Scanner) | Wireless Communications |

| Radar Systems         | Industrial                                           | Surgical Systems        |

Figure 6. Table of Common FPGA Applications (5)

## **2.1 FPGA Definitions**

The most common FPGA architecture consists of an array of logic blocks (generally called Configurable Logic Block (CLB), or Logic Array Block (LAB), I-O pads, and routing channels. To better understand the architecture, it is important to first define the terminology, listed below found within Zeidman's *Architecture of FPGAs and CPLDs: A Tutorial*.

| Term                               | Definition                                                                                                                                |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Configurable Logic<br>Block (CLB)  | Location of function calculations.                                                                                                        |

| DIOCK (CLD)                        |                                                                                                                                           |

| I/OB                               | The block that connects an FPGA to other elements of the application.                                                                     |

| Interconnect                       | Allows for the communication between IOB to CLB. It is the wiring resources in an FPD                                                     |

| Field-Programmable<br>Device (FPD) | Refers to an integrated circuit that can be configured by the<br>end user. Another name for FPDs is programmable logic<br>devices (PLDs). |

| Programmable Logic<br>Array (PLA)  | A small FPD that contains two, programmable levels of logic; an AND-plane and an OR-plane.                                                |

| SPLD                               | Refers to any type of <i>simple</i> PLD.                                                                                                  |

| CPLD                               | Refers to a <i>complex</i> PLD that consists of an arrangement of                                                                         |

Master Thesis by Susan Portugal

| <u>.</u>            | multiple SPLD-like blocks on a single chip.                                                                             |

|---------------------|-------------------------------------------------------------------------------------------------------------------------|

| Programmable        | A programmable switch that can connect a logic element to                                                               |

| Switch              | an interconnect wire, or one interconnect wire to another.                                                              |

| Logic Block         | A small circuit block that is replicated in an array in an FPD.                                                         |

| Logic Capacity      | The amount of digital logic that can be mapped into a single                                                            |

|                     | FPD, typically measured in units of "equivalent number of                                                               |

|                     | gates in a traditional gate array."                                                                                     |

| Speed Performance   | Measures the maximum operable speed of a circuit when                                                                   |

|                     | implemented in an FPD. It is set by the longest delay                                                                   |

|                     | through any path for combinational circuits and for                                                                     |

|                     | sequential circuits; it is the maximum clock frequency for                                                              |

|                     | which the circuit functions properly.                                                                                   |

| Lookup Table (LUT): | A lookup table is utilized to change the input data into a                                                              |

|                     | more desirable output format. This is used in data analysis,                                                            |

| Taull A J Jaco      | particularly in image processing.                                                                                       |

| Full Adder          | A logic element which operates on two binary digits and a                                                               |

|                     | carry digit from a preceding stage, producing as output a sum digit and a new carry digit. It is also known as a three- |

|                     | input adder.                                                                                                            |

| Flip-flop           | A circuit that has two stable states and can be used to store                                                           |

| пр пор              | state information. It can be made to change state by signals                                                            |

|                     | applied to one or more control inputs and will have one or                                                              |

|                     | two outputs. It is the basic storage element in sequential                                                              |

|                     | logic                                                                                                                   |

| Mux (Multiplexer)   | A device that selects one of several analog or digital input                                                            |

|                     | signals and forwards the selected input into a single line.                                                             |

|                     | They are primarily used to increase the amount of data that                                                             |

|                     | can be sent over the network, within a certain amount of                                                                |

|                     | time and bandwidth. It is also call a data selector. A mux                                                              |

|                     | also makes it possible for several signals to share one                                                                 |

|                     | device or resource.                                                                                                     |

Figure 7. Key Terms (6)

### 2.2 FPGA Architecture

Again, to re-iterate, the most common FPGA architecture consists of an array of logic blocks (generally called Configurable Logic Block (CLB), or Logic Array Block (LAB), I'O pads, and routing channels as shown below in Figure 8.

Figure 8. Typical FPGA Structure (7)

While the number of CLBs LABs and I/Os required is readily determined from the design, the number of routing tracks required may vary considerably. Since unused routing tracks increase the cost (and typically decreases performance) without providing any benefit, FPGA manufacturers try to provide just enough tracks so that most designs will fit in terms of lookup tables (LUTs) and I/Os that can be routed.

In general, a logic block (CLB or LAB) consists of a few logic cells. A typical cell consists of a 4-input LUT, a full adder (FA) and a D-type flip-flop, as shown below in Figure 9. In this figure, the LUTs are split into two 3-input LUTs. In *normal mode* those are combined into a 4-input LUT through the left mux. The selection of mode is programmed into the middle multiplexer. The output can be either synchronous or asynchronous, depending on the programming of the mux.

Figure 9. Basic Illustration of a Logic Cell (1)

A look-up table is simply a memory element, shown below in Figure 10. The output is determined by the state of the inputs.

Figure 10. LUT (8)

In recent years, manufacturers have started moving to 6-input LUTs in their high performance parts. Since clock signals (and often other high-fan-out signals) are typically routed by special-purpose, dedicated routing networks, the signals are managed separately.

CLBs are a very basic building block of the FPGA. The CLB is a useful way to describe the size of an FPGA; however, not all CLBs are the same. Figure 11, list three different FPGAs produced by Xilinx with the associated FPGAs on the Xilinx evaluation kits.

| <u> </u> |     |                                                             |

|----------|-----|-------------------------------------------------------------|

|          |     | Each CLB contains two slices:                               |

|          |     | • A CLB on a Virtex-5 FPGA contains the following:          |

|          |     | <ul> <li>Eight input lookup tables (LUT)</li> </ul>         |

|          |     | Eight flip-flops                                            |

|          |     | • A CLB on a Virtex-6 and Spartan 6 contains the following: |

|          |     | <ul> <li>Eight lookup tables (LUT)</li> </ul>               |

|          |     | 16 flip-flops                                               |

|          | *   | Virtex XC5VLX50T contains (Evaluation Kit \$1,195)          |

|          |     | • 7,200 Slices                                              |

|          | *   | Virtex XC6VLX240T contains (Evaluation Kit \$1,795)         |

|          |     | • 37,680 Slices                                             |

|          | *** | Spartan 6 XC6SLX16 contains (Evaluation Kit §295)           |

|          |     |                                                             |

Figure 11. Xilinx CLB Comparison

The I/O block structure contains input/output registers, control signals, muxes and clock signals as illustrated below in Figure 12.

Figure 12. I/O block structure (8)

An I/O Block, as shown above in Figure 12, is used to bring signals into the chip and back off again. It consists of an input buffer and an output buffer with three-state, and open, collector-output controls. Typically there are pull up resistors on the outputs, and pull down resistors that can be used to terminate signals and buses.

The FPGA clock manipulation can be implemented with a phase-locked loop (PLL) or a delay-locked loop (DLL). PLLs generate the desired phase or frequency output by a voltage-controlled oscillator. PLL's are characteristically, analog circuits. DLLs access signals from a calibrated tapped delay line circuit internal to the FPGA to produce the desired clock phase or frequency. DLLs are digital circuits. (8) Figure 13 depicts an overview of a basic FPGA architecture.

Figure 13. Basic FPGA Architecture (8)

# **Chapter 3: FPGA Management: Verilog and VHDL Software**

The performance or action of an FPGA is typically controlled or managed by a hardware description language (HDL). Presently, there are two widely used standard HDLs—VHDL and Verilog. VHDL was developed under contract for the US Department of Defense as a part of the Very-High-Speed Integrated Circuits (VHSIC) program and subsequently became an IEEE standard language. Verilog was developed by Gateway Design Automation in 1985. Verilog HDL is a hardware description language used to design and document electronic systems. Verilog HDL allows designers to design at various levels of abstraction. It is the most widely used HDL with a user community of more than 50,000 active designers. (9) The difference between the two languages is slight. The choice of language is mainly personal preference, tool availability, and the industry. In the United States, the commercial industries tend to use more Verilog, while the aerospace and defense industries weigh more heavily in favor of VHDL.

Verilog was a proprietary language, but eventually became an IEEE standard language. Another programming language now in use, being utilized with FPGA's has been marketed by National Instruments under the name of LabVIEW. LabVIEW is a graphical programming language that includes an FPGA add-in module, allowing to target and program FPGA hardware. Verilog is the hardware program utilized in the subject project. Figure 14 below is an example of a Boolean expression coded in VHDL and Verilog.

VHDL Code 2: $F \le (A \text{ and } B) \text{ nor } (C \text{ and } C)$ Verilog: $F \le (A \& B) | (C \& D)$

Figure 14. Diagram of Boolean Expression Represented in VHDL & Verilog (10)

Both the VHDL and Verilog code segments produce exactly the same hardware representation. (10)

# **Chapter 4: Pulse Monitor Project Details**

### 4.1 Pulse Monitor Overview

The designed FPGA application project is a pulse monitor. The main goal of the project is to measure the pulse width of a digital (Transistor-Transistor Logic) TTL input signal. A pulse monitor measures pulse width by detecting the rising and falling edge of a digital signal as shown below in Figure 15, and counts the duration of the pulse using the system clock. Using the Ethernet port (10/100/1000 Tri-Speed Ethernet PHY), data is passed between the FPGA circuit board to a GUI software program. (11) For monitoring multiple digital signals, the software program can send commands to the FPGA board to switch between different digital input pins and/or command a reset.

Figure 15. Digital Signal

Research went into the SP601, the FPGA circuit board involved in the project, to see whether or not it could prove to be a solution to cost effectiveness and results. It was found that this low cost solution would be beneficial where a high cost oscilloscope needed to be utilized, and yet would not be able to record data indefinitely, like the Pulse Monitor. Initially, there were several hurdles when using the provided SP601 Base Reference Design tutorial program. The SP601 Base Reference Design provides a User Guide (15) on how to operate the software, and how to download the bit file to the SP601 board, however there is no documentation for the actual Verilog or C $\ddagger$  code flow. Therefore the user is left to reverse engineer both the Verilog and C $\ddagger$  code.

### 4.2 Hardware

This project was developed using a Xilinx Spartan 6 FPGA SP601 Evaluation Kit using the XC6SLX16 CSG324-2C Spartan-6 FPGA logic chip which contains 14,579 logic cells as seen in Figure 16. (12)

Figure 16. Spartan-6 FPGA SP601 Evaluation Kit (11)

The Spartan-6 FPGA Evaluation Kit was a replacement to its predecessor, the Spartan 3E Starter Kit that contained a XC3S500E FPGA, encompassing 10,476 logic cells. (13)

There were three main reasons why this evaluation board was selected for this project. The first reason was the large number of slices as in comparison to its predecessor, the Spartan 3E. The second reason the Spartan 6 Evaluation Board was selected was due to price of the board at \$295, considered a very cost effective solution. And lastly, the Spartan 6 was chosen as it was the latest low cost FPGA produced by Xilinx at the time this project was initiated.

The specifications of the SP601 Evaluation Kit are shown below in Figure 17.

| FPGA:                                          |

|------------------------------------------------|

| XC6SLX16 CSG324-2C Spartan-6                   |

| Configuration:                                 |

| Onboard configuration circuitry                |

| 8MB Quad SPI Flash                             |

| 16MB Parallel (BPI) Flash                      |

| JTAG                                           |

| Memory:                                        |

| DDR2 Component Memory 128MB                    |

| IIC 8Kb IIC EEPROM                             |

| Communication:                                 |

| 10/100/1000 Tri-Speed Ethernet PHY             |

| Serial (UART) to USB Bridge                    |

| Expansion Connectors:                          |

| FMC LPC connector (68 single-ended or 34       |

| differential user defined signals)             |

| 8 User I/O (Digilent 2x6 Header)               |

| Clocking:                                      |

| 200MHz Oscillator (Differential)               |

| Socket (Single-Ended) Populated with 27MHz Osc |

| SMA Connectors (Differential)                  |

| Display:                                       |

| 4X LEDs                                        |

| Control:                                       |

| 4X Push Buttons                                |

| 4X DIP Switches                                |

Figure 17. SP601 Evaluation Kit Specifications (11)

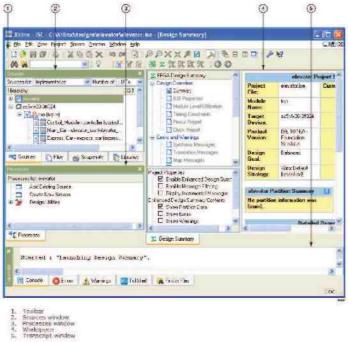

## 4.2.1 Hardware Code

The pulse monitor hardware program is written in Verilog and the project was designed using Xilinx's ISE Project Navigator. Project Navigator organizes all files within the project (similar to Visual Studio) and processes the project design for implementation for the desired targeted Xilinx device, as in Figure 18 below. (14) Within the Project Navigator, users are able to produce a bit stream to load their design onto the designated FPGA. To generate a bit stream, the Project Navigator steps through a few Key processes. The first process is "Synthesize XST" which synthesizes the project code, checking for errors. The second process is "Implement Design" which verifies the project meets the specified timing requirements and maps and routing occurs. The last process is "Generate Programming File" which is where the bit stream file is created to be loaded onto an FPGA. This project utilized the original Xilinx project tutorial that was created to aid users to get started with the Spartan 601 Starter Kit, as the starting point. Using the basic communication between the FPGA and GUI, the pulse width monitoring was added. (15)(16)

Master Thesis by Susan Portugal

Xilinx ISE Project Navigator (14) Figure 18.

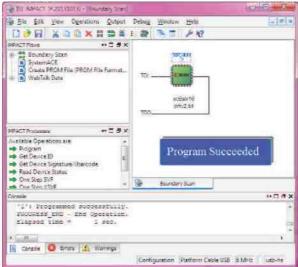

Within the ISE Design Suite, ISE iMPACT software (Figure 19) is used to program the PFGA with the bit stream that was created within the ISE Project Navigator software. ISE iMPACT software allows users to "Initialize Chain," which detects the type of FPGA connected to the computer and therefore load their desired design. This software also allows users to create a PROM file to be loaded into the EEPROM memory. Once the evaluation board is flashed with the created PROM file, the board will power-cycle with the same design.

Figure 19. Xilinx ISE iMPACT

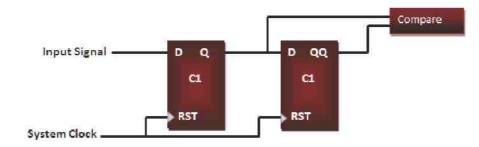

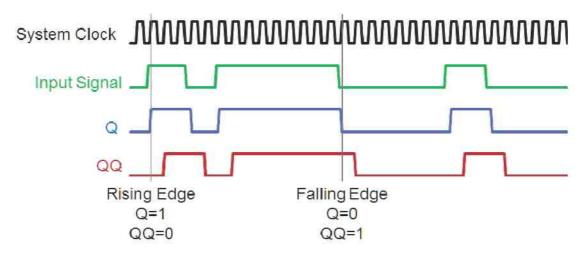

The sequential steps begin within the top level, main module of the source code which the pulse width is measured off the positive edge of the 125 MHz input clock. With the aid of two D flip-flops, the input pulse edge is detected. This is shown in Figure 20 below. The first D flip-flop synchronizes the input signal (pulse\_in\_q1) and the second D flip-flop stage is used for the edge detection (pulse\_in\_qq1). Next, values are compared for detecting a rising edge or a falling edge of the input signal. If either event occurs, the pulse width 32 bit integer counter value is saved and the counter is reset. Otherwise, if the signal neither rises nor falls, the counter increments. (17)

Figure 20. Edge Detection by D Flip-Flops (17)

Figure 21 is a timing diagram example to show how the D flip-flops are used for edge detection. The first black line is the system clock and the second green line is an example input signal. Using the system clock as a rest, the second D flip-flop (red line) holds the value of the input signal and the first D flip-flop (blue line) holds the current value of the input signal. Both d flip-flops are evaluated and set on the positive edge of the system clock. Therefore, as seen in Figure 21, for a rising edge, Q is equal to 1 and QQ is equal to 0 and QQ is equal to 1 for a falling edge detection.

Figure 21. Pulse Monitor Example Input Timing Diagram

## 4.2.2 Verilog Code

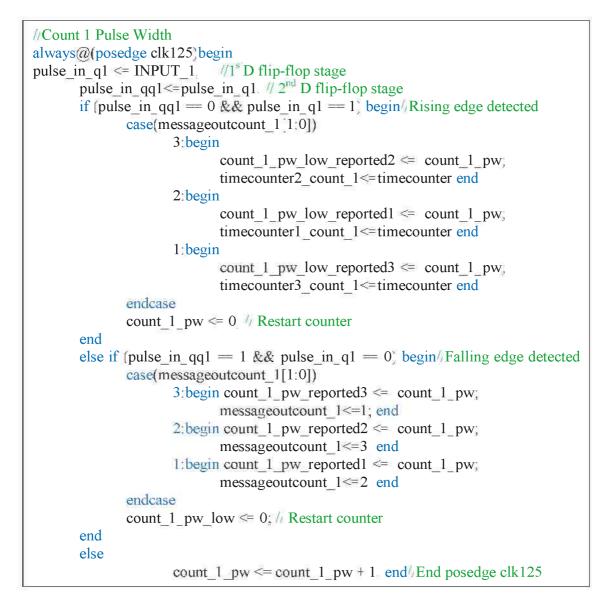

The following Verilog code snippet in Figure 22 below shows the edge detection which is executed every positive edge of the 125 MHz system clock. The first D flip-flop stage is assigned the value of the input signal (INPUT\_1). The next line takes in the second stage of the D flip-flop for comparison. After the two stages of the flip-flops acquire their values, the two values are compared to detect either a rising edge, falling edge, or continue counting. If the comparison results in a rising or falling edge, the counter value is saved in one of the three saved counter 32 bit integer. Each reported pulse represented by the counter saves the high value, low value, and system clock counter. The system clock counter is used by the GUI to insure the order of the input signal. To allow high frequency input signals, and remove the possibility of losing data, the Pulse Monitor saves the last three pulses of data for one input channel. Three pulses per input signal were chosen due to the size of the message sent between the FPGA and C<sup>‡</sup> GUI.

Figure 22. Verilog Code for Edge Detection

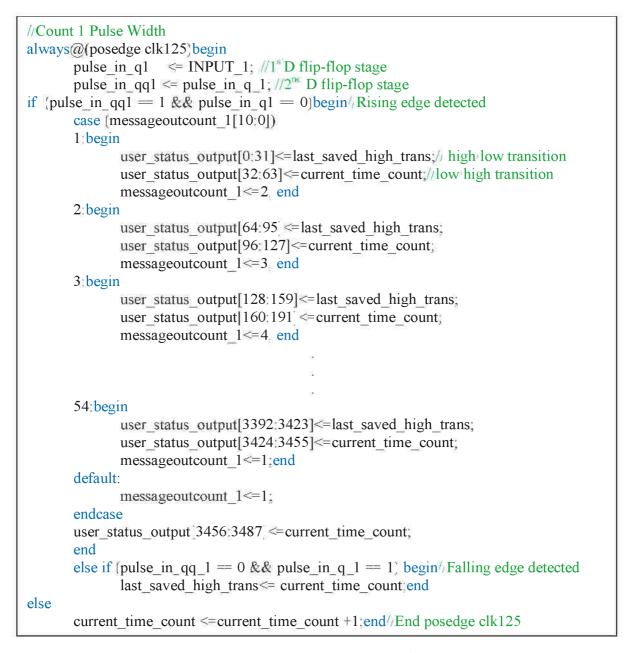

The following Verilog code snippet in Figure 23 below shows that depending upon the user's desired channel selection, the user status message array is filled with three pulses of data and a time count for organization on the software side. If the FPGA receives a 0 command, each channel's counter and the overall time counter is reset to zero.

```

case(user ctrl en[7:0])//channel selected by user

8 user status <= {count 8 pw reported1 count 8 pw low reported1 timecounter1 count 8,

count 8 pw reported2 count 8 pw low reported2 timecounter2 count 8,

count 8 pw reported3 count 8 pw low reported3 timecounter3 count 8,

timecounter ::

1 user status <= {count 1 pw reported1 count 1 pw low reported1 timecounter1 count 1,

count 1 pw reported2 count 1 pw low reported2 timecounter2 count 1,

count 1 pw reported3 count 1 pw low reported3, timecounter3 count 1,

timecounter};

0 begin

count 1 pw \leq 0;

count 2 pw<=0;

count 3 pw<=0;

count 4 pw<=0;

count 5 pw \leq 0;

count 6 pw \le 0;

count 7 pw \leq 0;

count_8_pw<=0;

timecounter \leq 0;

user status \leq \{1111, 80 \, d0\};

end

default user status \leq 1010 \ 80 \ d0;

endcase

```

Figure 23. Verilog Code for Channel Selection for Output Message

Although Figure 22 and Figure 23 show the main Verilog code that was inserted into the provided tutorial project it took substantial trial and error effort to get to this point.

In addition to detecting the rise and fall of the input digital signal the tutorial program also needed to be enhanced by sending a larger packet of data between the FPGA and the GUI than the original 16 byte per message format. Originally the FPGA sent 16 bytes of data based upon receiving a 1 or 0 from the GUI. The GUI would receive the message and decode the result to be either hello or goodbye. To accommodate the additional data, the message was expanded to 40 bytes.

| <u>Original</u> | reg 127.0 user_status=0 | 4 16 bytes |

|-----------------|-------------------------|------------|

| Pulse Monitor   | reg 319.0 user_status=0 | 🅢 40 bytes |

The main module monitors the input channels and then the data is pushed to the Ethernet packet engine module that fills the FIFO to be sent to the GUI. Just as the main module was modified to accommodate a larger data register of 40 bytes the Ethernet packet engine module was therefore modified to accommodate the new message size. The

receiving buffer on the GUI side also needed to be expanded to accept the new message and decode the message received. If there is a mismatch of message size, either no data will be transferred or the GUI will not be able to handle the message received.

567:0]tx shift=0 *II* holds up to 71 bytes of packet data reg Original tx shift <= {SERVER MAC, MY MAC 16 d20, OP USER CONTROL+8h80, USER CTRL EN USER CTRL USER STATUS 296 d0}; **Pulse Monitor:** tx shift <= SERVER MAC MY MAC 16 d20. OP\_USER\_CONTROL+8 h80 {USER\_CTRL\_EN\_USER\_CTRL\_USER\_STATUS}, 80 d0};

## 4.3 Software Code

The Pulse Monitor GUI is programmed in C<sup>#</sup> with Visual Studio 2010. With the aid of SharpPcap.Packet winPcap library, the Pulse Monitor sends and filters received User Datagram Protocol (UDP) messages from the FPGA. The Ethernet packet is structured so that it allows for one-to-one communication between the GUI and the FPGA; however, multiple programs can be setup to listen to the messages from the FPGA although only one program sending commands to the FPGA is desired. This also allows for multiple FPGAs to be setup on the same network for multiple nested combinations of communications.

## 4.3.1 Visual Studio C# Code

The Ethernet packet is structured with an array of data with header and desired commands. The header contacts a MAC address of the FPGA it is communicating to. Therefore, the FPGA only filters in messages sent with its MAC address in the header of the Ethernet message. After the MAC address is filtered, the FPGA responds to the type of message received, such as status or user defined channel. This low level raw Ethernet package, is sent between the GUI and FPGA due to the FPGA lack of a Network Interface Card (NIC). Lastly, the control word designates which channel the user is requesting data from. Figure 24 below defines the Ethernet packet sent from the PC to the FPGA.

wPcapDevice.SendPacket(CreateEthernetPacket(xilinxDeviceMac, newbyte[4] {

(byte)OPCODE.USER\_DEFINED, control, controlWord[0], controlWord[1] }));

### Figure 24. C# Send Packet (16)

When a message is received from the FPGA, the GUI insures that the message was received from the FPGA and processes the message depending upon what type of data is received; status or user defined pulse data. Figure 25 below shows how the PC filters the Ethernet packet and sorts by message type.

```

byte[] addressBytes = newbyte[7];

Array.Copy(packet.Bytes_6, addressBytes, 0, 6);

MACaddr = newMAC(addressBytes);

if (addr Value = xilinxDeviceMac Value)

return;

if (packet Data[0] == (byte)OPCODE.STATUS_RESPONSE)

ProcessStatusResponse(packet Data);

elseif (packet Data[0] == (byte)OPCODE USER_DEFINED_RESPONSE)

ProcessUserDefinedResponse(packet Data);

```

Figure 25. C Ethernet Filter and Message Type Filter (16)

Once the desired response is obtained, the data from the FPGA is converted to double and multiplied by 8 to convert from 125 MHz count values to time in nanoseconds. The FPGA system clock is 125MHz which means that each clock cycle is: 1/125MHz=0.00000008s=8ns.

The GUI of the Pulse Monitor, in Figure 26 below, allows the user to select a desired input channel. The status of the FPGA will be populated within the Pulse Width Status text box. A connection status is located at the bottom of the GUI to notify users of connection status between the FPGA and the PC. The figure below demonstrates two scenarios; the first is a 10Hz input signal with a 50.0<sup>1</sup>/<sub>4</sub> duty cycle and the second is a 1 kHz input signal with a 15<sup>9</sup>/<sub>4</sub> duty cycle.

| A/ Paler Montor                                      | Contraction of the second s | W Nate Montes                                                        |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| File Sitio Hels                                      |                                                                                                                 | The Setal Help                                                       |

|                                                      | Pulse<br>Monitor                                                                                                | Pulse<br>Monitor                                                     |

| Monitor   Restord Setup:<br>Sugnal Solicidos Contest |                                                                                                                 | Mentini Becard Salapi<br>Signal Senoton Coultrol                     |

| Chaseel                                              | 123355555                                                                                                       | Causer 1 2 3 4 5 5 7 8<br>+ 0 0 0 0 0 0 0 0                          |

| 6                                                    | Clase Al Mar Values                                                                                             | Clines Ad Main Values                                                |

| Status                                               |                                                                                                                 | Inte                                                                 |

| Puter triati<br>Hight: Silms                         | Low1: 200000.51 ms                                                                                              | Pater Weth Low 1: 0186ms<br>High 1/ 0.15mm<br>Tiwer 1: 040040.345 mm |

| High 2 20ms -                                        | Low2: 5000                                                                                                      | High2: 0.15mm<br>Timer2: 859379.18 ces                               |

| High3: 50ms                                          | Low3: 30452-85 ms                                                                                               | HighO, G. 15mm<br>Tanandi, 872290,84 mm                              |

| Current Computer                                     | Term: 122112012 1223 11 PM                                                                                      | Current Computer Teller 1021001213311 IB-PM                          |

| Convention Statum<br>Link: Convention Put            | ter Monitor                                                                                                     | Connecting Statue<br>Carrier Connected to Pulse Monten               |

Figure 26. Pulse Monitor GUI

## **4.4 Pulse Monitor Enhancements**

Using the basic building block of the Pulse Monitor, additional versions were created as new requirements were developed based upon the initial release of the Pulse Monitor, resulting in enhanced capabilities and performance. The initial Pulse Monitor monitors eight channels individually and saves only one channel of data at a time. After the Release of the first version of the Pulse Monitor, the following new requirements were developed to meet the needs of the users:

- Monitor eight channels simultaneously

- Allow users to view all eight channels simultaneously

- Save data for up to eight channels simultaneously

- Allow for monitoring differential input signals

- Monitor higher frequency input signal

- Post processing encoded signals

There were three versions of the Pulse Monitors to cover all of the new requirements. The first version improves upon the initial design by allowing simultaneous channel monitoring. The second version also allows simultaneous channel monitoring, and with the addition of the FMCX105 debugs card, allows for differential signal inputs. The third version only allows one channel input, but can sample the input signal at a higher frequency.

## 4.4.1 Multi-Channel Single Ended Input Signal Pulse Monitor

The initial design of the Pulse Monitor was first enhanced due to the need of monitoring more than one channel simultaneously. A maximum of eight channels was selected to be monitored due to hardware limitations of the FPGA J13 header pin out; 12 I/O (Input/Output) header with the following configuration: 8 I/O header pins, 2 ground pins, and 2 VCC pins. Figure 27 highlights the J13 header pin circled in red.

Master Thesis by Susan Portugal

Figure 27. SP601 Evaluation Board with J13 Circled in Red

This design of the Pulse Monitor uses 10,638 slice registers of 18,224 available, which is 58% of the usable amount of slices on the SP601 FPGA. The Verilog code was enhanced in two areas. The user status messages, an array in the top module, was expanded to allow more data to be sent from the FPGA to the GUI, and the FIFO array (register tx\_shift), in the Ethernet packet engine module was expanded to fit eight channels of data as seen in Figure 28.

| User Status Message Change:         |                                                     |

|-------------------------------------|-----------------------------------------------------|

| Original Pulse Monitor:             | Multi-Channel Pulse Monitor:                        |

| reg 319.0]user_status=0,// 40 bytes | reg [319:0]user_status_output1=0; // 40 bytes       |

|                                     | reg [319:0]user_status_output2=0; // 40 bytes       |

|                                     | reg [319:0]user_status_output3=0 // 40 bytes        |

|                                     | reg [319:0]user_status_output4=0 // 40 bytes        |

|                                     | reg [319:0]user_status_output5=0 // 40 bytes        |

|                                     | reg [319:0]user_status_output6=0 // 40 bytes        |

|                                     | reg [319:0]user_status_output7=0; // 40 bytes       |

|                                     | reg [319:0]user_status_output8=0 // 40 bytes,       |

|                                     |                                                     |

|                                     | Total of 320 bytes of data                          |

| FIFO Array (tx_shift) Change:       |                                                     |

| Original Pulse Monitor:             | Multi-Channel Pulse Monitor:                        |

| reg [567:0]tx_shift=0; // 71        | reg [4991.0]tx_shift=0; // 624 bytes of packet data |

| bytes of packet data                | $tx_shift \leq {SERVER_MAC, MY_MAC 16 d20,}$        |

| tx_shift <= {SERVER_MAC,            | OP_USER_CONTROL+8 h80,                              |

| MY_MAC,16 d20,                      | {USER_CTRL_EN USER_CTRL,                            |

| OP_USER_CONTROL+8 h80,              | USER_STATUS1, USER_STATUS2,                         |

| {USER_CTRL_EN USER_CTRL,            | USER_STATUS3 USER_STATUS4 USER_STATUS5,             |

| USER_STATUS} 72 d0};                | USER_STATUS6,                                       |

| 8 A                                 | USER_STATUS7 USER_STATUS8 2032 d0;;                 |

|                                     | Filmer G Filmer 4t 10,0                             |

Figure 28. Verilog Changes for Multi-Channel Pulse Monitor

The GUI message handler was also changed within the C# project, to receive a larger packet of data and parse accordingly as seen in Figure 29. The original pulse monitor only allowed for a packet length of 40 bytes of data which was changed to a dynamic length determined upon the received messaged; a minimum of 20 bytes is required to process the message. The dynamic length is also implemented to allow for future growth.

```

privatevoid ProcessUserDefinedResponse(byte[ packet)

{

if (packet Length < 20)

return;

Queue<byte> response = newQueue<byte>();

for (int i = 1 i < packet Length; i++)//originally:for (int i = 1 i <40 i++)

response Enqueue(packet[i]);

UpdateUserStatus(response ToArray());

}

</pre>

```

### Figure 29. Visual Studio C# Changes for Multi-Channel Pulse Monitor

| The GUI was also changed visually to allow users to view all eight of    | channels of data |

|--------------------------------------------------------------------------|------------------|

| simultaneously utilizing eight control lists as seen below in Figure 30. |                  |

|            |                |            |           | P          | ulse       |           |            |              |           |           |                   |

|------------|----------------|------------|-----------|------------|------------|-----------|------------|--------------|-----------|-----------|-------------------|

| Manitor Re | cord Setup     |            |           | ,          | Mon        | itor      |            |              |           |           |                   |

| hannel 1   |                |            | Channel 2 |            |            | Channel 3 |            |              | Channel 4 |           |                   |

| High (me)  | Low (ms)       | Timer (ms) | High (ms) | Low (me)   | Timer (ma) | High (ma) | Low (me)   | Tintter (ma) | High (ma) | Low (rss) | Timer (me)        |

| 5          | 5              | 11852.744  | 8         | 4          | 37882.604  | 8.5       | 35         | 18392.546    | 25        | 7.5       | 27882 388         |

| 5          | 5              | 11842.744  | 4         | 4          | 37672.804  | 5.5       | 3.6        | 18387 546    | 2.5       | 75        | 27547 388         |

| Б          | 5              | 11832.744  | 6         | 4          | 37682.604  | 0.5       | 35         | 16372.546    | 2.5       | 7.5       | 27632 388         |

| 5          | 5              | 11822.744  | 6         | 4          | 37652.604  | 6.5       | 35         | 18362,546    | 2.5       | 7.5       | 27622 388         |

| 5          | 5              | 11812,744  | 6         | 4          | 37642.604  | 8.5       | 35         | 18352 548    | 2.5       | 7.5       | 27612.388         |

| 5          | 5              | 11802.744  | 0         | 18         | 37632,604  | 5.5       | 3.0        | 183/2.647    | 25        | 7.5       | 27002388          |

| Б          | 5              | 11702.744  | 8         | 4          | 37822 605  | 8.5       | 3.5        | 18332.547    | 2.5       | 7.5       | 27502 388         |

| Б          | 5              | 11782.744  | 6         | 4          | 37512 505  | 65        | 3.5        | 18322.547    | 25        | 7.6       | 27582388          |

| 5          | 5              | 11772.744  | 6         | 1          | 37802 605  | 8.5       | 35         | 18312.547    | 2.5       | 7.5       | 27572.388         |

| 5          | 5              | 11762.744  | 6         | 4          | 37592.605  | 6.5       | 3.5        | 20302.547    | 2.5       | 7.5       | 27562 388         |

| <          | 1              |            | 1.        | m          |            | • • •     | N.         | A PROPERTY A | (f.).     | M.        | and the second of |

| Channel 5  |                |            | Channel 6 |            |            | Channel 7 |            |              | Channel 8 |           |                   |

| High (ms)  | Low (ms)       | Timer (ms) | High (ma) | Low (ms)   | Timer (ms) | High (ma) | Low (ms)   | Timer (ms)   | High (ms) | Low (ms)  | Timer (ms)        |

| 85         | 0.5            | 38302.222  | 37        | 63         | 23892.137  | 2.8       | 7.4        | 20151 995    | 1.8       | 8.4       | 33161.87          |

| 25         | 0.5            | 38292 222  | 37        | 6.3        | 23882.137  | 2.8       | 2.4        | 30141.995    | 1.8       | 8.4       | 33151.87          |

| 95         | 0.5            | 38292 222  | 37        | 8.2        | 23872 137  | 2.6       | 7.4        | 30131 995    | 1.6       | 8.4       | 331/1.87          |

| 0.5        | 0.5            | 38272 222  | 37        | 8.3        | 23962 137  | 2.6       | 7.4        | 30121 096    | 1.6       | 84        | 33131.87          |

| 95         | 0.5            | 38262 222  | 37        | 6.3        | 23852 137  | 26        | 74         | 30111.095    | 1.6       | 8.4       | 33121.87          |

| 9.5        | 0.5            | 38252 222  | 37        | 6.3        | 23842138   | 2.6       | 7.4        | 30101.995    | 1.6       | 8.4       | 31111.07          |

| 9.5        | 0.5            | 30242.222  | 3.7       | 6.3        | 23032.130  | 2.6       | 7.4        | 30091 995    | 1.6       | 5.4       | 33101.87          |

| 95         | 3.5            | 38292.222  | 37        | 6.3        | 23622.138  | 2.6       | 7.4        | 30081 995    | 1.6       | \$4       | 33991 37          |

| 8.5        | 0.5            | 38222.222  | 3.7       | 6.3        | 23812.138  | 2.6       | 7.4        | 30071.995    | 1.6       | 8.4       | 33081.87          |

| 9.5        | 0.5            | 38212.222  | 3.7       | 6.5        | 23802138   | 2,6       | 7.4        | 30081 995    | 1.6       | 8.4       | 33071.87          |

| 91         |                |            | 3.0       | 18         |            | i (#10    | THE SECOND |              | 1         | 10        |                   |

|            |                |            |           |            |            |           |            |              |           |           |                   |

| Controls   |                |            |           | Record     |            |           |            |              |           |           |                   |

| 1          | Clear All Time | 015        | 1         | Step Reque | aline)     |           |            | Record       | Clais     |           |                   |

|            |                |            |           |            |            |           |            |              |           |           |                   |

Figure 30. Multi-Channel Pulse Monitor GUI

## 4.4.2 Multi-Channel Differential Input Signal Pulse Monitor

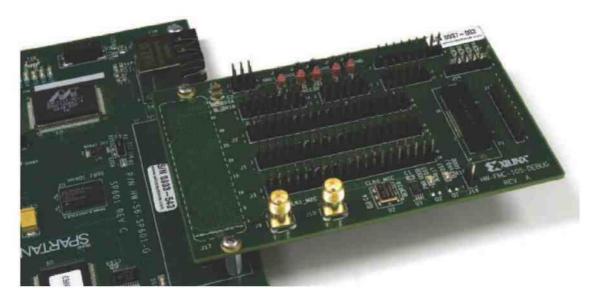

Another expansion upon the original one channel and multi-channel pulse monitor was the need for monitoring differential signals simultaneously. Differential input signals are very effective in canceling out any outside noise that may be present in the surrounding environment. (18)In implementing eight differential input signals, modifications to both Verilog code and hardware were required. The input signals were remapped to accommodate a positive and negative input per channel for the VITA 57.1 FMC-LPC input connector. In order to connect to the input signals on the VITA 57.1 FMC-LPC input connector a Xilinx FMCXM105 Debug Card seen in Figure 31 was necessary in aiding to the addition of I/O pins that are not easily assessable on the SP601 Evaluation Board. There is only one GPIO HDR (General Purpose Input Output Header) pin-out located on the SP601 Evaluation Board which allows for eight I/O pin connections. This design of the Pulse Monitor uses 10,858 slice registers of 18,224 available, which is 59% of the usable amount of slices on the SP601 FPGA.

Figure 31. Xilinx FMC XM105 Debug Card (Cost: \$159) (19)

Using Spartan-6 Libraries Guide for HDL Designs provided by Xilinx, the following change in Figure 32 was implemented to convert two signal differential inputs to an internal output buffer. Within the IDBUDS, a design level interface signal is represented as two distinct ports (I and IB), one is deemed the "master" and the other is the "slave." For the Pulse Monitor, INPUT\_1\_P(P for positive) is I, INPUT\_1\_N(N for negative) is IB, and INPUT\_1 is the output buffer. (20)

// IBUFDS: Differential Input Buffer // Spartan-6 // Xilinx HDL Libraries Guide, version 12.4 IBUFDS #( DIFF\_TERM("FALSE"), // Differential Termination IOSTANDARD("DEFAULT") // Specify the input I/O standard ) IBUFDS\_inst ( .O(INPUT\_1), // Buffer output It(INPUT\_1\_p) // Diff\_p buffer input (connect directly to top-level port) IB(INPUT\_1\_n) // Diff\_n buffer input (connect directly to top-level port) ); // End of IBUFDS\_inst instantiation

Figure 32. Differential Input Verilog Code (20)

In addition to the changes made to implement differential inputs, changes to the User Constraints File (UCF) were required to reroute the input signal channels seen in Figure 33. The ucf file is an ASCII file that defines the project's constraints of the logical design. (21)

| Original Pulse Monitor:<br>NET 'INPUT 1' LOC = | N17":  | Multi-Channel Pulse Monitor:<br>NET 'INPUT 1 n' LOC = 'C8"; |

|------------------------------------------------|--------|-------------------------------------------------------------|

| NET 'INPUT_2' LOC =                            | M18",  | $NET 'INPUT_1_p' LOC = D8";$                                |

| NET 'INPUT_3' LOC =                            | 'A3";  | NET 'INPUT_2_n' LOC = $A12$ ;                               |

| NET 'INPUT_4' LOC =                            | 'L15"; | NET 'INPUT_2_p' LOC = 'B12'';                               |

| NET 'INPUT_5' LOC =                            | F15";  | NET 'INPUT_3_n' LOC = $"C6";$                               |

| NET 'INPUT_6' LOC =                            | 'B4";  | NET 'INPUT_3_p' LOC = $'D6''$ ;                             |

| NET 'INPUT_7' LOC =                            | F13";  | NET 'INPUT_4_n'' LOC = 'A11'';                              |

| NET 'INPUT_8' LOC =                            | P12";  | NET 'INPUT_4_p' LOC = 'B11'';                               |

|                                                |        | NET 'INPUT_5_n' LOC = $A2^{*}$ ;                            |

|                                                |        | NET 'INPUT_5_p' LOC = 'B2'';                                |

|                                                |        | NET 'INPUT_6_n' LOC = "F9";                                 |

|                                                |        | NET 'INPUT_6_p' LOC = "G9";                                 |

|                                                |        | NET 'INPUT_7_n' LOC = $A7''$                                |

|                                                |        | NET 'INPUT_7_p' LOC = $'C7"$ ;                              |

|                                                |        | NET 'INPUT_8_n' LOC = $P7''$ ;                              |

|                                                |        | NET 'INPUT_8_p' LOC = 'N6";                                 |

Figure 33. UCF Changes for Multi-Channel Pulse Monitor

The following Figure 34 references the FPGA Pin to the Schematic Net Name which is used in reference Figure 35 to correlate the appropriate pin on FMC XM105 J1Connector.

| J1 FMC<br>LPC Pin | Sebamatic diat Mena |     | J1 FMC<br>LPC Pin | Schematic Nrt Name | Ut FPGA<br>Pin |  |

|-------------------|---------------------|-----|-------------------|--------------------|----------------|--|

| C10               | FMC_LAM_P           | D12 | Di                | FMC PWR COOD FLAS  | 83             |  |

| CII               | FMC LABEN           | C12 | D8                | FMC_LA01_CC_P      | DII            |  |

| C14               | PMC_LAMP            | DS  | D9                | PMC LATE OC N      | C11            |  |

| C15               | FMC_LAI0_N          | C8  | DII               | FMC_LAS_P          | #14            |  |

| C18               | EMC_LA14_P          | B2  | D12               | FMC_LA05_N         | A14            |  |

| C19               | FMC_LAI4_N          | A2  | D14               | FMC_LA09_P         | GI             |  |

| C22               | FMC_LA18_CC_P       | R10 | D15               | EMC_LA09_N         | F10            |  |

| C23               | EMC_LAIS_CC_N       | T10 | D17               | FMC_LA13_P         | 811            |  |

| C26               | PMC_LA27_P          | R1I | Dis               | FMC_LAB_N          | All            |  |

| C27               | FMC_LA27_N          | TII | 1020              | FMC_LAI7_CC_P      | RS             |  |

| C30               | IIC_SCL_MAIN        | P11 | 1021              | FMC_LAI7_CC_N      | 18             |  |

| C31               | IIC_SDA_MAIN        | NIO | D23               | FMC_LA23_P         | NS             |  |

|                   |                     |     | D.14              | FMC_LA23_N         | P6             |  |

|                   |                     |     | D26               | FMC_LA26_P         | U7             |  |

|                   |                     |     | 1027              | FMC_LA26_N         | 17             |  |

| 62                | FMC CLK1 M2C P      | Te  | HZ                | FMC PRSNT MDC L    | U13            |  |

| G                 | FMC CLK1 M2C N      | V9  | 14                | PMC CLK0 M2C P     | CIU            |  |

| 66                | PMC LA00 CC P       | 109 | HIS               | FMC CLK0 M2C N     | A10            |  |

| 67                | FMC LAR CC N        | C9  | HP                | FMC LA02 P         | CIS            |  |

| C9                | FMC LAG P           | C13 | EIS               | FMC_LA02_N         | A15            |  |

| G10               | FMC LA03 N          | AIJ | H10               | FMC LA04 P         | BIG            |  |

| G12               | FMC LA09 P          | Fit | HII               | PMC LA04 N         | A16            |  |

| G13               | FMC_LA08_N          | Ell | H13               | FMC_LA07_P         | E7             |  |

| G15               | FMC_LA32_P          | D6  | H14               | FMC_LA07_N         | E\$            |  |

| G16               | FMC_LA12_N          | C6  | H16               | FMC_LAI1_P         | 812            |  |

| GIS               | FMC_LAt6_P          | G   | HI7               | FMC_LAII_N         | A12            |  |

| G19               | FMC_LA16_N          | A7  | -H19              | FMC_LA15_P         | G9             |  |

| G21               | FMC_LA20_P          | N7  | H20               | FMC_LA15_N         | In             |  |

| G22               | FMC LA20 N          | P8  | H22               | FMC_LAI9_P         | Nió            |  |

| G24               | EMC LA22 P          | R7  | 1123              | FMC LA19 N         | 17             |  |

Figure 34. VITA 57.1 FMC LPC Connections on SP601 Spartan Evaluation Board (Desired pins selected in blue) (21)

| FMC HPC<br>Connector<br>J17 Pin | Signal Name                  | J1<br>Connector<br>(Odd Pins) | FMC-NPC<br>Consector<br>J17 Pin | Signal Name                 | Ji<br>Connector<br>(Even Pins) |  |

|---------------------------------|------------------------------|-------------------------------|---------------------------------|-----------------------------|--------------------------------|--|

| G6 FMC_LAUD_CC_P                |                              | 1                             | CH                              | FMC_LAIO_P                  | 2                              |  |

| -62                             | FMC LAID CC_N[1]             | 3                             | C15                             | FMC_LA10_N                  | 4                              |  |

| D8                              | FMC LARLCE P(I)              | 5                             | - H16                           | FMC_LAIL_P_                 | 6                              |  |

| 1D4                             | PMC LAUL CC N <sup>(1)</sup> | 7                             | H 7                             | FMC LAIL N                  | 8                              |  |

| HI                              | FMC_LA02_P                   | . 9                           | G15                             | FMC_LAI2_P                  | 10                             |  |

| 116                             | FMC_LA02_N                   | -11                           | -G16                            | FMC_LAI2_N                  | 12                             |  |

| -63                             | FMC_LA03_P                   | 13                            | .D17                            | FMC_LAI2_P                  | 14                             |  |

| G10                             | FMC_LA03_N                   | 15                            | D18                             | FMC LAB N                   | 16                             |  |

| 1110                            | HID FMC_LAOLP                |                               | C18                             | FMC_LAH, P                  | 18                             |  |

| 1411                            | FMC_LA04_N                   | 19                            | . C19                           | EMC_LAH_N                   | 20                             |  |

| 1911                            | PMC_LA05_P                   | 21                            | H19                             | FMC_LAIS_P                  | 22                             |  |

| <b>彩</b> 柱2                     | EMC_LAIS_N                   | 23                            | H20                             | PMC LASS N                  | 24                             |  |

| C10                             | FMC LA05 F                   | 25                            | C18                             | FMC LAI6 P                  | 26                             |  |

| CH                              | CH FMC_LA05_N                |                               | G19                             | PMC LASE N                  | 28                             |  |

| 8413                            | HIJ PMC LAUT P               |                               | D20                             | FMC_LAD_CC_Pub              | 30                             |  |

| 1914                            | PMC_LA07_N                   | .28                           | D21                             | FMC_LAI7_CC_N <sup>ID</sup> | 32                             |  |

| C12                             | FMC_LA08_F                   | 13                            | 6.22                            | FMC_LAIS_CC_JED             | 34                             |  |

| GI3                             | FMC_LA08_N                   | 35                            | C21                             | FMC LAIS CC ND              | 30                             |  |